Product Summary

The EP610ILC-10 Altera ClassicTM device offers a solution to high-speed, lowpower logic integration. Fabricated on advanced CMOS technology, EP610ILC-10 also has a Turbo-only version. The EP610ILC-10 supports 100% TTL emulation and can easily integrate multiple PAL- and GAL-type devices with densities ranging from 300 to 900 usable gates.

Parametrics

EP610ILC-10 absolute maximum ratings: (1)Supply voltage With respect to ground, VCC: –2.0 to 7.0V; (2)DC input voltage, VI: –0.5 to VCC+0.5V; (3)DC VCC or ground current, IMAX: -175 to 175mA; (4)DC output current, per pin, IOUT: -25 to 25mA; (5)Storage temperature No bias, TSTG: –65 to 150℃; (6)Ambient temperature Under bias, TAMB: –65 to 135℃; (7)Junction temperature Ceramic packages, under bias, TJ: 150℃; (8)Plastic packages, under bias: 135℃.

Features

EP610ILC-10 features: (1)Complete device family with logic densities of 300 to 900 usable gates; (2)Device erasure and reprogramming with non-volatile EPROM configuration elements; (3)Fast pin-to-pin logic delays as low as 10 ns and counter frequenciesas high as 100 MHz; (4)Programmable security bit for protection of proprietary designs; (5)100% generically tested to provide 100% programming yield; (6)Programmable registers providing D, T, JK, and SR flipflops with individual clear and clock controls.

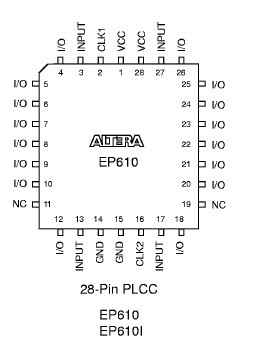

Diagrams

|

EP610I |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)